DFN6 2x2, 0.65P CASE 506DT ISSUE O

**DATE 31 JUL 2016**

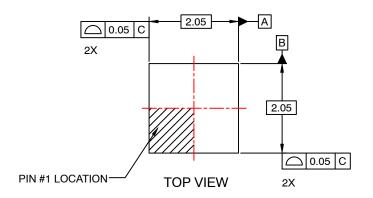

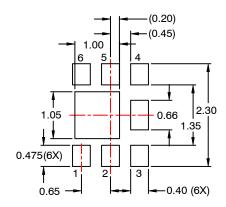

RECOMMENDED LAND PATTERN

| Pin# | Function |

|------|----------|

| 1    | Drain    |

| 2    | Drain    |

| 3    | Gate     |

| 4    | Source   |

| 5    | Drain    |

| 6    | Drain    |

| 7    | Drain    |

| 8    | Source   |

|      |          |

| <del></del>                                                  |

|--------------------------------------------------------------|

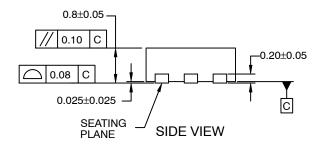

| 0.90±0.10 +-                                                 |

| (0.200) 4X (0.15)                                            |

| PIN #1 IDENT (0.50)<br>1 2 3 (0.30)                          |

| 0.265±0.065<br>(6X)  0.265±0.065  7  8  1.00±0.05  2.05±0.05 |

| 1.30 0.10 M C A B                                            |

| BOTTOM VIEW                                                  |

## NOTES:

- A. PACKAGE DOES NOT CONFORM TO ANY JEDEC STANDARD.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 2009.

- D. LAND PATTERN RECOMMENDATION IS EXISTING INDUSTRY LAND PATTERN.

| DOCUMENT NUMBER: | 98AON13616G     | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | DFN6 2X2, 0.65P |                                                                                                                                                                                     | PAGE 1 OF 1 |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.